### Peripheral Hardware Ch. 5

ECE331 rev: Spring 2013

ECE 331, Prof. A. Mason

ASM Programming p.1

### Outline

- Preview 689HC12 peripheral blocks

- I/O addressing schemes

- Configuration registers

- I/O ports

- "Modes of operation"

- External memory interface

- Memory cells, types, arrays

### **68HC12** Peripheral Blocks

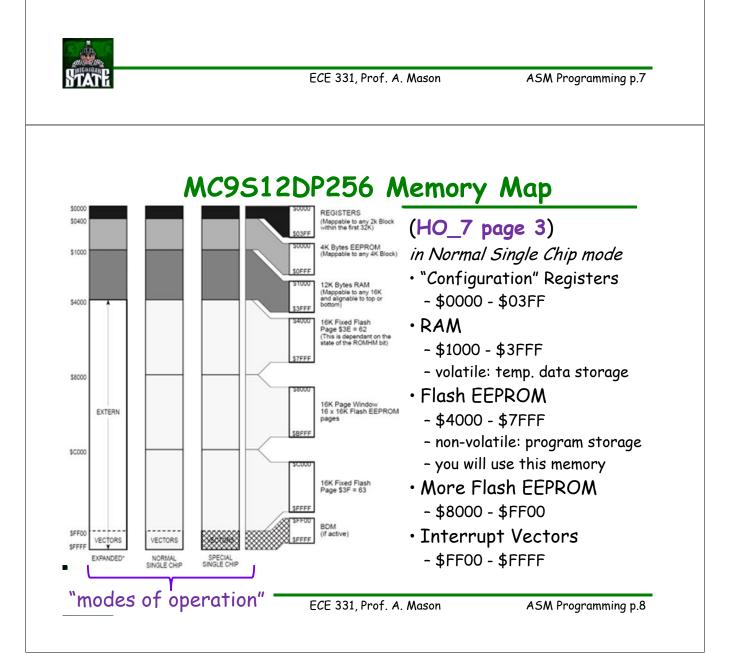

### Memory Map Architecture

#### • Detailed Architecture (68HC12)

- s per byte - CPU w/ HC12 register file data **Central Processing Unit** (temporary) · connection details added Memory **Control Unit** CCR program Control PC - Buses address IR (non--SP volatile) data d + n=8 data lines instruction data d • m=16 address lines Register configuration File - Memory & I/O registers ALU data RAM **I/O Devices** 5 Buses (ports) program PROM Data Path memory map configuration registers & ports all "mapped" to 2<sup>m</sup> addresses

- $\cdot \rightarrow$  memory map = assignment of addresses to different memory blocks

- Configuration Registers

- microcontroller memory registers containing function control signals

- EX: enable/disable interrupts, set timer speed, etc.

- port control and port data registers

- Port = external input/output signals; interface to outside of microcontroller

ECE 331, Prof. A. Mason

ASM Programming p.5

# I/O Addressing Schemes

How does software talk to peripherals?

- Two common "addressing schemes"

- -vary with  $\mu C$  brand

### •<u>Memory Mapped I/O</u>

- -address bus size determines max size of memory

- -memory partitioned into 2 functional blocks

- user memory (for program/data bytes)

- SRAM, EEPROM, Flash EEPROM

- $\cdot$  I/O register memory (for control of I/O peripheral functions)

- SRAM or FF registers (volatile: lose value when no power)

- -HC12 is memory mapped scheme

## I/O Addressing Schemes

### •<u>Isolated I/O</u>

-separate set of addresses for a) memory and b) I/O registers

- -requires additional control signal to select from a) & b)

- M/IO: 0=I/O, 1=Memory

-Intel (and others) use isolated I/O scheme

### Pros/Cons of Isolated I/O

- ⊙ more addresses available for I/O devices

- ⊙ no memory space lost to I/O devices

- 🛞 require extra control signal (pin) in addition to addr. bus

### **Configuration Registers**

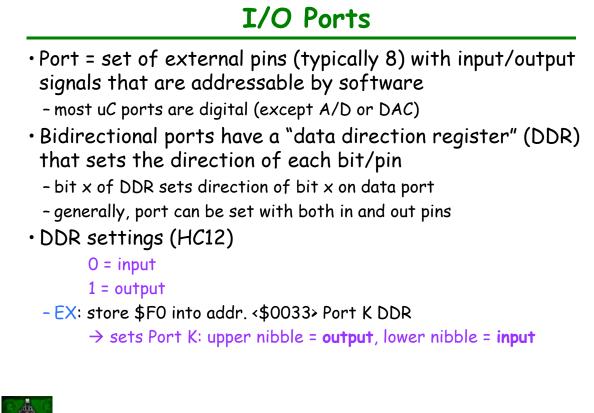

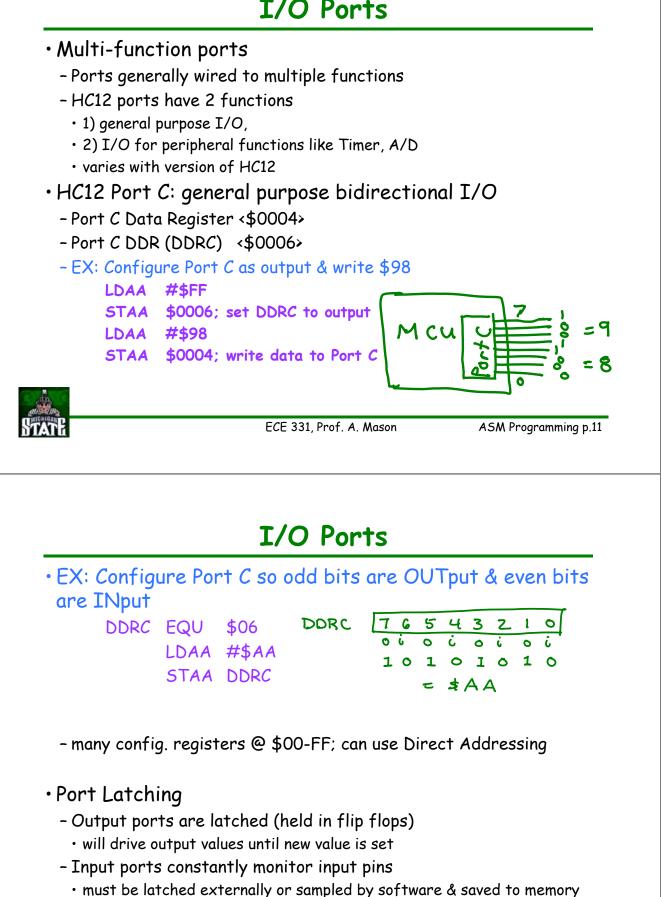

### I/O Ports

• otherwise might capture wrong data if not synchronized correctly

### Modes of Operation

- HC12/S12 has 8 operating modes

- selected by pins MODC, MODB, MODA

| MODC                     | MODB      | MODA   | Mode                    | Port A    | Port B    |

|--------------------------|-----------|--------|-------------------------|-----------|-----------|

| 0                        | 0         | 0      | special single chip     | G.P. I/O  | G.P. I/O  |

| 0                        | 0         | 1      | special expanded narrow | Addr/Data | Addr      |

| 0                        | 1         | 0      | special peripheral      | Addr/Data | Addr/Data |

| 0                        | 1         | 1      | special expanded wide   | Addr/Data | Addr/Data |

| 1                        | 0         | 0      | normal single chip      | G.P. I/O  | G.P. I/O  |

| 1                        | 0         | 1      | normal expanded narrow  | Addr/Data | Addr      |

| 1                        | 1         | 0      | reserved                |           |           |

| 1                        | 1         | 1      | normal expanded wide    | Addr/Data | Addr/Data |

| $G_{\cdot}P_{\cdot} = 0$ | oeneral d | urbose | ·                       |           |           |

- 3 "normal" modes

- some config. registers are protected (can't read/write)

- 4 "special" modes

- can access all config. registers

- used to test uC; not for typical use

ECE 331, Prof. A. Mason

ASM Programming p.13

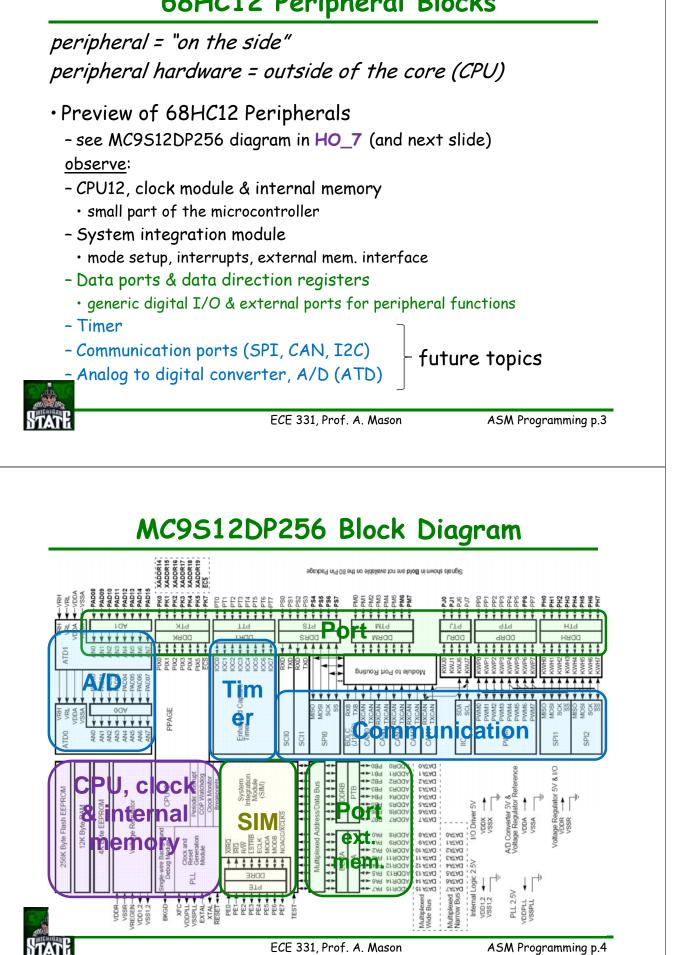

## Normal Operating Modes

HCS12 (what you use in lab)

- <u>Single Chip</u>: all I/O ports are available for general use - mode we will use in lab

- <u>Expanded Wide</u>: Ports A&B used for Addr & Data bus

- wide = 16 bit data bus

- multiplexed: address one cycle, data next cycle

- Expanded Narrow: Port A & B are address bus (16b)

#### HC12

• Uses Ports A, B, C, D rather than multiplexing A&B

### **Expanded Modes**

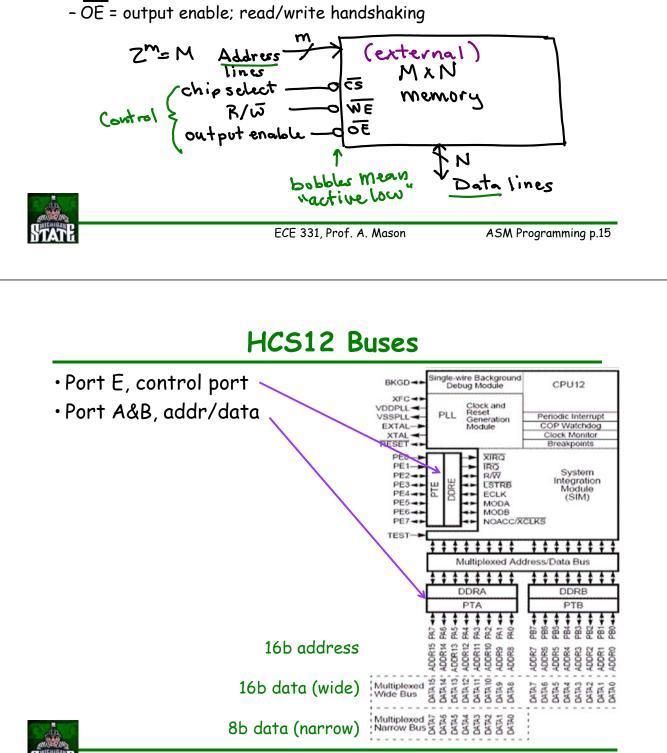

- Used for interfacing to <u>external</u> memory-mapped components (memory or I/O devices)

- Requires Address, Data & Control buses

#### control bus

- $\overline{CS}$  = active low chip select; selects from multiple external devices

- $-\overline{WE}$  = write enable