## ASM Instructions

### **Functional Instruction Groups**

- Data Transfer/Manipulation

- Arithmetic

- Logic & Bit Operations

- Data Test

- Branch

- Function Call (Subroutine)

## Data Transfer/Manipulation

| Mnemonic                  | Function                | Operation      | С | V | Ζ | N |

|---------------------------|-------------------------|----------------|---|---|---|---|

| LDAA                      | Load accumulator A      | A ← M          |   | 0 | Δ | Δ |

| LDAB                      | Load accumulator B      | B ← M          |   | 0 | Δ | Δ |

| LDD                       | Load accumulator D      | A ← M, B ← M+1 |   | 0 | Δ | Δ |

| LDX                       | Load index register X   | X ← M:M+1      |   | 0 | Δ | Δ |

| LDY                       | Load index register Y   | Y ← M:M+1      |   | 0 | Δ | Δ |

| LDS                       | Load stack pointer (SP) | SP ← M:M+1     |   | 0 | Δ | Δ |

| Table A Load instructions |                         |                |   |   |   |   |

#### Table A. Load instructions

| Mnemonic | Function                 | Operation                            | С | V | Ζ | Ν |

|----------|--------------------------|--------------------------------------|---|---|---|---|

| STAA     | Store accumulator A      | $A \rightarrow M$                    |   | 0 | Δ | Δ |

| STAB     | Store accumulator B      | $B \rightarrow M$                    |   | 0 | Δ | Δ |

| STD      | Store accumulator D      | $A \rightarrow M, B \rightarrow M+1$ |   | 0 | Δ | Δ |

| STX      | Store index register X   | $X \rightarrow M:M+1$                |   | 0 | Δ | Δ |

| STY      | Store index register Y   | $Y \rightarrow M:M+1$                |   | 0 | Δ | Δ |

| STS      | Store stack pointer (SP) | $SP \rightarrow M:M+1$               |   | 0 | Δ | Δ |

#### Table B. Store instructions

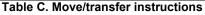

| Mnemonic | Function                  | Operation                                  | С | V | Ζ | Ν |

|----------|---------------------------|--------------------------------------------|---|---|---|---|

| TAB      | Transfer acc. A to acc. B | B←A                                        |   | 0 | Δ | Δ |

| TBA      | Transfer acc. B to acc. A | A ← B                                      |   | 0 | Δ | Δ |

| TAP      | Transfer acc. A to CCR    | CCR ← A                                    | Δ | Δ | Δ | Δ |

| TPA      | Transfer CCR to acc.A     | A ← CCR                                    | 1 |   | 1 | - |

| MOVB     | Mem to Mem move byte      | $(M)_1 \rightarrow (M)_2$                  | 1 | - | ł |   |

| MOVW     | Mem to Mem move Word      | (M:M+1) <sub>1</sub> →(M:M+1) <sub>2</sub> |   |   |   |   |

|                               | Logical shift instr            | uctions                                                                                    |  |  |

|-------------------------------|--------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Mnemonic                      | Function                       | Operation                                                                                  |  |  |

| LSL <opr></opr>               | Logical shift left memory      |                                                                                            |  |  |

| LSLA                          | Logical shift left A           |                                                                                            |  |  |

| LSLB                          | Logical shift left B           |                                                                                            |  |  |

| LSLD                          | Logical shift left D           | $\begin{array}{c c} \bullet & \bullet \\ \hline C & b7 & A & b0 & b7 & B & b0 \end{array}$ |  |  |

| LSR < opr>                    | Logical shift right memory     |                                                                                            |  |  |

| LSRA                          | Logical shift right A          |                                                                                            |  |  |

| LSRB                          | Logical shift right B          | b7 b0 C                                                                                    |  |  |

| LSRD                          | Logical shift right D          | $0 \xrightarrow{b7} A \xrightarrow{b0} b7 \xrightarrow{b7} B \xrightarrow{b0} C$           |  |  |

| Arithmetic shift instructions |                                |                                                                                            |  |  |

| Mnemonic                      | Function                       | Operation                                                                                  |  |  |

| ASL <opr></opr>               | Arithmetic shift left memory   |                                                                                            |  |  |

| ASLA                          | Arithmetic shift left A        |                                                                                            |  |  |

| ASLB                          | Arithmetic shift left B        | C 07 00                                                                                    |  |  |

| ASLD                          | Arithmetic shift left D        | C b7 A b0 b7 B b0                                                                          |  |  |

| ASR <opr></opr>               | Arithmetic shift right memory  |                                                                                            |  |  |

| ASRA                          | Arithmetic shift right A       |                                                                                            |  |  |

| ASRB                          | Arithmetic shift right B       | b7 b0 C                                                                                    |  |  |

|                               | Rotate instruct                | tions                                                                                      |  |  |

| Mnemonic                      | Function                       | Operation                                                                                  |  |  |

| ROL <opr></opr>               | Rotate left memory thru carry  |                                                                                            |  |  |

| ROLA                          | Rotate left A through carry    | < <u>□</u> < <u>□</u>                                                                      |  |  |

| ROLB                          | Rotate left B through carry    | C b7 b0                                                                                    |  |  |

| ROR <opr></opr>               | Rotate right memory thru carry |                                                                                            |  |  |

| RORA                          | Rotate right A through carry   | →□────→                                                                                    |  |  |

| RORB                          | Rotate right B through carry   | b7 b0 C                                                                                    |  |  |

Table 2.7

Summary of shift and rotate instructions

### Shift/Rotate CCR Actions:

• C= $\Delta$ , V= $\Delta$ , Z= $\Delta$ , N= $\Delta$  (except LSR where N=0)

## Arithmetic

| Mnemon                         | Function                   | Operation              | Η | С | V | Ζ | Ν |

|--------------------------------|----------------------------|------------------------|---|---|---|---|---|

| ABA                            | Add acc. A and acc. B      | A ← A+B                | Δ | Δ | Δ | Δ | Δ |

| ABX                            | Add acc. B to index reg. X | X ← B+X                | Δ | Δ | Δ | Δ | Δ |

| ABY                            | Add acc. B to index reg. Y | Y ← B+Y                | Δ | Δ | Δ | Δ | Δ |

| ADDA                           | Add acc. A with memory     | A ← A+M                | Δ | Δ | Δ | Δ | Δ |

| ADDB                           | Add acc. B with memory     | B ← B+M                | Δ | Δ | Δ | Δ | Δ |

| ADDD                           | Add acc. D with memory     | $D \leftarrow D+M:M+1$ | - | Δ | Δ | Δ | Δ |

| ADCA                           | ADDA with carry            | A ← A+M+C              | Δ | Δ | Δ | Δ | Δ |

| ADCB                           | ADDB with carry            | B ← B+M+C              | Δ | Δ | Δ | Δ | Δ |

| Table D. Addition instructions |                            |                        |   |   |   |   |   |

Table D. Addition instructions

| Function                    | Operation                                                                                                                                    | С                                                                                                                                                                                                                                                     | V                                                                                                                                                                                                                                                                             | Ζ                                                                                                                                                                                                                                                                                                                               | N                                                                                                                                                                                                                                                                                                                                                                            |

|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Subtract acc. B from acc. A | A ← A-B                                                                                                                                      | Δ                                                                                                                                                                                                                                                     | Δ                                                                                                                                                                                                                                                                             | Δ                                                                                                                                                                                                                                                                                                                               | Δ                                                                                                                                                                                                                                                                                                                                                                            |

| Subtract memory from acc. A | A ← A-M                                                                                                                                      | Δ                                                                                                                                                                                                                                                     | Δ                                                                                                                                                                                                                                                                             | Δ                                                                                                                                                                                                                                                                                                                               | Δ                                                                                                                                                                                                                                                                                                                                                                            |

| Subtract memory from acc. B | B ← B-M                                                                                                                                      | Δ                                                                                                                                                                                                                                                     | Δ                                                                                                                                                                                                                                                                             | Δ                                                                                                                                                                                                                                                                                                                               | Δ                                                                                                                                                                                                                                                                                                                                                                            |

| Subtract memory from acc. D | D ← D-M:M+1                                                                                                                                  | Δ                                                                                                                                                                                                                                                     | Δ                                                                                                                                                                                                                                                                             | Δ                                                                                                                                                                                                                                                                                                                               | Δ                                                                                                                                                                                                                                                                                                                                                                            |

| SUBA with borrow            | A ← A-M-C                                                                                                                                    | Δ                                                                                                                                                                                                                                                     | Δ                                                                                                                                                                                                                                                                             | Δ                                                                                                                                                                                                                                                                                                                               | Δ                                                                                                                                                                                                                                                                                                                                                                            |

| SUBB with borrow            | B ← B-M-C                                                                                                                                    | Δ                                                                                                                                                                                                                                                     | Δ                                                                                                                                                                                                                                                                             | Δ                                                                                                                                                                                                                                                                                                                               | Δ                                                                                                                                                                                                                                                                                                                                                                            |

|                             | Subtract acc. B from acc. A<br>Subtract memory from acc. A<br>Subtract memory from acc. B<br>Subtract memory from acc. D<br>SUBA with borrow | Subtract acc. B from acc. A $A \leftarrow A - B$ Subtract memory from acc. A $A \leftarrow A - M$ Subtract memory from acc. B $B \leftarrow B - M$ Subtract memory from acc. D $D \leftarrow D - M : M + 1$ SUBA with borrow $A \leftarrow A - M - C$ | Subtract acc. B from acc. AA $\leftarrow$ A-B $\Delta$ Subtract memory from acc. AA $\leftarrow$ A-M $\Delta$ Subtract memory from acc. BB $\leftarrow$ B-M $\Delta$ Subtract memory from acc. DD $\leftarrow$ D-M:M+1 $\Delta$ SUBA with borrowA $\leftarrow$ A-M-C $\Delta$ | Subtract acc. B from acc. A $A \leftarrow A-B$ $\Delta$ $\Delta$ Subtract memory from acc. A $A \leftarrow A-M$ $\Delta$ $\Delta$ Subtract memory from acc. B $B \leftarrow B-M$ $\Delta$ $\Delta$ Subtract memory from acc. D $D \leftarrow D-M:M+1$ $\Delta$ $\Delta$ SUBA with borrow $A \leftarrow A-M-C$ $\Delta$ $\Delta$ | Subtract acc. B from acc. A $A \leftarrow A-B$ $\Delta$ $\Delta$ $\Delta$ Subtract memory from acc. A $A \leftarrow A-M$ $\Delta$ $\Delta$ $\Delta$ Subtract memory from acc. B $B \leftarrow B-M$ $\Delta$ $\Delta$ $\Delta$ Subtract memory from acc. D $D \leftarrow D-M:M+1$ $\Delta$ $\Delta$ $\Delta$ SUBA with borrow $A \leftarrow A-M-C$ $\Delta$ $\Delta$ $\Delta$ |

Table E. Subtraction instructions

| Mnemonic | Function              | Operation | С | V | Ζ | N |

|----------|-----------------------|-----------|---|---|---|---|

| DEC      | Decrement memory by 1 | M ← M-1   |   | Δ | Δ | Δ |

| DECA     | Decrement A by 1      | A ← A-1   |   | Δ | Δ | Δ |

| DECB     | Decrement B by 1      | B ← B-1   |   | Δ | Δ | Δ |

| DES      | Decrement SP by 1     | SP ← SP-1 |   |   | Δ |   |

| DEX      | Decrement X by 1      | X ← X-1   |   |   | Δ |   |

| DEY      | Decrement Y by 1      | Y ← Y-1   |   |   | - |   |

Table F. Decrement instructions

| Mnemonic | Function              | Operation | С | V | Ζ | Ν |

|----------|-----------------------|-----------|---|---|---|---|

| INC      | Increment memory by 1 | M ← M+1   |   | Δ | Δ | Δ |

| INCA     | Increment A by 1      | A ← A+1   |   | Δ | Δ | Δ |

| INCB     | Increment B by 1      | B ← B+1   |   | Δ | Δ | Δ |

| INS      | Increment SP by 1     | SP ← SP+1 |   |   | Δ |   |

| INX      | Increment X by 1      | X ← X+1   |   |   | Δ |   |

| INY      | Increment Y by 1      | Y ← Y+1   |   | 1 |   | - |

**Table G. Increment instructions**

# Logic & Bit Operations

| Mnemonic          | Function                             | Operation                          |

|-------------------|--------------------------------------|------------------------------------|

| ANDA <opr></opr>  | AND A with memory                    | $A \leftarrow (A) \bullet (M)$     |

| ANDB <opr></opr>  | AND B with memory                    | $B \leftarrow (B) \bullet (M)$     |

| ANDCC <opr></opr> | AND CCR with memory (clear CCR bits) | $CCR \leftarrow (CCR) \bullet (M)$ |

| EORA <opr></opr>  | Exclusive OR A with memroy           | $A \leftarrow (A) \oplus (M)$      |

| EORB <opr></opr>  | Exclusive OR B with memory           | $B \leftarrow (B) \oplus (M)$      |

| ORAA <opr></opr>  | OR A with memory                     | $A \leftarrow (A) + (M)$           |

| ORAB < opr>       | OR B with memory                     | $B \leftarrow (B) + (M)$           |

| ORCC <opr></opr>  | OR CCR with memory                   | $CCR \leftarrow (CCR) + (M)$       |

| CLC               | Clear C bit in CCR                   | C ← 0                              |

| CLI               | Clear I bit in CCR                   | I ← 0                              |

| CLV               | Clear V bit in CCR                   | $V \leftarrow 0$                   |

| COM <opr></opr>   | One's complement memory              | $M \leftarrow $ \$FF - (M)         |

| COMA              | One's complement A                   | A ← \$FF - (A)                     |

| COMB              | One's complement B                   | B ← \$FF - (B)                     |

| NEG < opr>        | Two's complement memory              | M ← \$00 - (M)                     |

| NEGA              | Two's complement A                   | A ← \$00 - (A)                     |

| NEGB              | Two's complement B                   | B ← \$00 - (B)                     |

Table 2.8 ■ Summary of Boolean logic instructions

| Mnem                                                                                                                                                                                                                                                                                    | onic        | Function             | Operation                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------|---------------------------------------|

| BCLR <o< td=""><td>opr&gt;², msk8</td><td>Clear bits in memory</td><td><math display="block">M \gets (M) \bullet (\overline{mm})</math></td></o<>                                                                                                                                       | opr>², msk8 | Clear bits in memory | $M \gets (M) \bullet (\overline{mm})$ |

| BITA <or< td=""><td>pr&gt;¹</td><td>Bit test A</td><td>(A) ● (M)</td></or<>                                                                                                                                                                                                             | pr>¹        | Bit test A           | (A) ● (M)                             |

| BITB < o                                                                                                                                                                                                                                                                                | pr>1        | Bit test B           | (B) ● (M)                             |

| BSET <o< td=""><td>ppr&gt;², msk8</td><td>Set bits in memory</td><td><math display="block">M \gets (M) + (mm)</math></td></o<>                                                                                                                                                          | ppr>², msk8 | Set bits in memory   | $M \gets (M) + (mm)$                  |

| <ul> <li>Note.</li> <li>1. <opr> can be specified using all except relative addressing modes for BITA and BITB.</opr></li> <li>2. <opr> can be specified using direct, extended, and indexed (exclude indiriect) addressing modes.</opr></li> <li>3. msk8 is an 8-bit value.</li> </ul> |             |                      |                                       |

Table 2.9 Summary of bit operations

### Logic CCR Actions:

- AND/OR/EOR: V=0, Z= $\Delta$ , N= $\Delta$  (except AND/OR CC)

- COM/COMA/COMB: C= 1, V=0, Z=Δ, N=Δ

- NEG/NEGA/NEGB: C= Δ, V=Δ, Z=Δ, N=Δ

- BITA/BITB/BCLR/BSET: V=0, Z= $\Delta$ , N= $\Delta$

### Data Test

| Compare instructions |                               |                |  |

|----------------------|-------------------------------|----------------|--|

| Mnemonic             | Function                      | Operation      |  |

| CBA                  | Compare A to B                | (A) - (B)      |  |

| CMPA                 | Compare A to memory           | (A) - (M)      |  |

| СМРВ                 | Compare B to memory           | (B) - (M)      |  |

| CPD                  | Compare D to memory           | (D) - (M:M+1)  |  |

| CPS                  | Compare SP to memory          | (SP) - (M:M+1) |  |

| CPX                  | Compare X to memory           | (X) - (M:M+1)  |  |

| CPY                  | Compare Y to memory           | (Y) ~ (M:M+1)  |  |

|                      | Test instructions             |                |  |

| Mnemonic             | Function                      | Operation      |  |

| TST                  | Test memory for zero or minus | (M) - \$00     |  |

| TSTA                 | Test A for zero or minus      | (A) - \$00     |  |

| TSTB                 | Test B for zero or minus      | (B) - \$00     |  |

Table 2.4

Summary of compare and test instructions

### Data Test CCR Actions:

- Compare:  $C= \Delta$ ,  $V=\Delta$ ,  $Z=\Delta$ ,  $N=\Delta$

- TST/TSTA/TSTB: C= 0, V=0, Z=Δ, N=Δ

### Branch

BVC

#### Unconditional Branches

| Unconditional Branches      |               |                     |  |  |  |

|-----------------------------|---------------|---------------------|--|--|--|

| Mnemonic                    | Function      | Comment             |  |  |  |

| BRN                         | branch never  | useful as delay     |  |  |  |

| BRA                         | branch always | 8-bit signed offset |  |  |  |

| Simple Conditional Branches |               |                     |  |  |  |

| Mnemonic                    | "if" Function | Condition = Flag    |  |  |  |

| BCC                         | carry clear   | C=0                 |  |  |  |

| BCS                         | carry set     | C=1                 |  |  |  |

| BEQ                         | equal         | Z=1                 |  |  |  |

| BNE                         | not equal     | Z=0                 |  |  |  |

| BMI                         | minus         | N=I                 |  |  |  |

| BPI                         | plus          | N=0                 |  |  |  |

| BVS                         | overflow set  | V=1                 |  |  |  |

|                             |               |                     |  |  |  |

#### **Unsigned Conditional Branches**

V=0

overflow clear

| Mnemonic | "if" Function  | Condition  | Flags |

|----------|----------------|------------|-------|

| BHS      | higher or same | $r \geq 0$ | C=0   |

| BHI      | higher than    | r > 0      | C+Z=0 |

| BLS      | lower or same  | $r \leq 0$ | C+Z=1 |

| BLO      | lower than     | r < 0      | C=1   |

#### Signed Conditional Branches

| Mnemonic   | "if" Function    | Condition  | Flags   |

|------------|------------------|------------|---------|

| BGE        | greater or equal | $r \geq 0$ | N⊕V=0   |

| BGT        | greater than     | r > 0      | Z+N⊕V=0 |

| BLE        | less or equal    | $r \le 0$  | Z+N⊕V=1 |

| BLT        | less than        | r < 0      | N⊕V=1   |

| r – requit |                  |            |         |

r = result

All branch instructions have a "long" version with 16-bit offset. For example, LBRA or LBCC.

CCR Actions: Branches do not effect CCR

## **Function Call (Subroutine)**

| Mnemonic | Function               | Operation                  | SP     |

|----------|------------------------|----------------------------|--------|

| JSR      | Jump to subtroutine    | PC ← M:M+1                 | ← SP-2 |

| RTS      | Return from subroutine | PC $\leftarrow$ M(SP:SP+1) | ← SP+2 |

|          |                        |                            |        |

CCR Actions: Subroutine calls do not effect CCR

## 68HC12 Addressing Modes

| Addressing Mode                               | Source Format                                     | Abbreviation | Description                                                                                                             |

|-----------------------------------------------|---------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|

| Inherent                                      | INST                                              | INH          | Operands (if any) are in CPU registers.                                                                                 |

| Immediate                                     | INST # <i>opr8i</i><br>or<br>INST # <i>opr16i</i> | IMM          | Operand is included in instruction stream.<br>8- or 16-bit size implied by context                                      |

| Direct                                        | INST opr8a                                        | DIR          | Operand is the lower 8 bits of an address in the range \$0000-\$00FF.                                                   |

| Extended                                      | INST opr16a                                       | EXT          | Operand is a 16-bit address                                                                                             |

| Relative                                      | INST <i>rel8</i><br>or<br>INST <i>rel16</i>       | REL          | An 8-bit or 16-bit relative offset from the current pc is supplied in the instruction.                                  |

| Indexed<br>(5-bit offset)                     | INST oprx5,xysp                                   | IDX          | 5-bit signed constant offset from x, y, sp, or pc                                                                       |

| Indexed<br>(auto pre-decrement)               | INST oprx3,-xys                                   | IDX          | Auto pre-decrement x, y, or sp by 1 ~ 8                                                                                 |

| Indexed<br>(auto pre-increment)               | INST oprx3,+xys                                   | IDX          | Auto pre-increment x, y, or sp by 1 ~ 8                                                                                 |

| Indexed<br>(auto<br>post-decrement)           | INST oprx3,xys–                                   | IDX          | Auto post-decrement x, y, or sp by 1 ~ 8                                                                                |

| Indexed<br>(auto post-increment)              | INST oprx3,xys+                                   | IDX          | Auto post-increment x, y, or sp by 1 $\sim$ 8                                                                           |

| Indexed<br>(accumulator offset)               | INST abd,xysp                                     | IDX          | Indexed with 8-bit (A or B) or 16-bit (D) accumulator offset from x, y, sp, or pc                                       |

| Indexed<br>(9-bit offset)                     | INST oprx9,xysp                                   | IDX1         | 9-bit signed constant offset from x, y, sp, or pc<br>(lower 8-bits of offset in one extension byte)                     |

| Indexed<br>(16-bit offset)                    | INST oprx16,xysp                                  | IDX2         | 16-bit constant offset from x, y, sp, or pc<br>(16-bit offset in two extension bytes)                                   |

| Indexed-indirect<br>(16-bit offset)           | INST [oprx16,xysp]                                | [IDX2]       | Pointer to operand is found at<br>16-bit constant offset from x, y, sp, or pc<br>(16-bit offset in two extension bytes) |

| Indexed-indirect<br>(D accumulator<br>offset) | INST [D, <i>xysp</i> ]                            | [D,IDX]      | Pointer to operand is found at<br>x, y, sp, or pc plus the value in D                                                   |

## Indexed Addressing Mode Operations

| Postbyte<br>Code (xb) | Source Code<br>Syntax  | Comments<br>rr: 00 = X, 01 = Y, 10 = SP, 11 = PC                                                                                                                                                 |

|-----------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| rr0nnnnn              | ,r<br>n,r<br>-n,r      | <b>5-bit constant offset</b> n = −16 to +15<br>r can specify x, y, sp or pc                                                                                                                      |

| 111rr0zs              | n,r<br>-n,r            | Constant offset (9- or 16-bit signed)<br>z:0 = 9-bit with sign in LSB of postbyte(s)<br>1 = 16-bit<br>if z = s = 1, 16-bit offset indexed-indirect (see below)<br>rr can specify x, y, sp, or pc |

| 111rr011              | [n,r]                  | <b>16-bit offset indexed-indirect</b><br>rr can specify x, y, sp, or pc                                                                                                                          |

| rr1pnnnn              | n,-r n,+r<br>n,r- n,r+ | Auto pre-decrement/increment<br>or Auto post-decrement/increment;<br>p = pre-(0)  or post-(1), n = -8  to  -1, +1  to  +8<br>rr can specify x, y, or sp (pc not a valid choice)                  |

| 111rr1aa              | A,r<br>B,r<br>D,r      | Accumulator offset (unsigned 8-bit or 16-bit)<br>aa:00 = A<br>01 = B<br>10 = D (16-bit)<br>11 = see accumulator D offset indexed-indirect<br>rr can specify x, y, sp, or pc                      |

| 111rr111              | [D,r]                  | Accumulator D offset indexed-indirect<br>rr can specify x, y, sp, or pc                                                                                                                          |

## Indexed Addressing Mode Operations & Examples

| Indexed Addressing Mode           | Offset       | Reference    | Source Code Example | Machine Code | Cycles |

|-----------------------------------|--------------|--------------|---------------------|--------------|--------|

| 5-bit signed constant offset      | -16+15       | X, Y, SP, PC | LDAA 15,X           | A6 0F        | 3      |

| 9-bit signed constant offset      | -256+255     | X, Y, SP, PC | LDAA 255,Y          | A6 E8 FF     | 3      |

| 16-bit signed constant offset     | -32768+65535 | X, Y, SP, PC | LDAA 4096,PC        | A6 FA 10 00  | 4      |

| 8-bit accumulator (A or B) offset | accA, accB   | X, Y, SP, PC | LDAA B,SP           | A6 F5        | 3      |

| 16-bit accumulator offset         | accD         | X, Y, SP, PC | LDAA D,X            | A6 E6        | 3      |

| Auto Pre-Increment by +1+8        | 18           | X, Y, SP     | LDAA 8,+SP          | A6 A7        | 3      |

| Auto Pre-Decrement by -18         | -18          | X, Y, SP     | LDAA 8,-Y           | A6 68        | 3      |

| Auto Post-Increment by +1+8       | 18           | X, Y, SP     | LDAA 1,X+           | A6 30        | 3      |

| Auto Post-Decrement by -18        | -18          | X, Y, SP     | LDAA 4,X-           | A6 3C        | 3      |

| 16-bit offset indexed-indirect    | -32768+65535 | X, Y, SP, PC | LDAA [4096,X]       | A6 E3 10 00  | 6      |

| D accumulator indexed-indirect    | accD         | X, Y, SP, PC | LDX [D,PC]          | EE FF        | 6      |

adapted from "Introducing the MC68HC12" by James M. Sibigtroth, http://elmicro.com/files/intro\_mc68hc12.pdf

## HC12 ASM Directives

EQU equates symbol with numeric valve -use to define memory location or constant -assembler replaces label with correct # value EX: LIST FQU \$5B

EX: LIST EQU \$5B defines variable 'LIST' = \$5B

- ORG origin: set memory address of instructions/data that follow -all programs must specific their ORG EX: TOP ORG \$6000 sets program origin at \$6000

- **END** set end of program -any ASM instructions following END are ignored -can have directives after END

- SWI software interrupt -stops program execution -use while testing/debugging code

- **RMB** reserve block of memory EX: TEMP BMP \$10 reserves 16 (\$10) bytes starting at addr. assigned to label TEMP

- **FCB** form constant byte

-reserves block of memory & initiates contents of reserved block EX: ABC FCB \$11, \$12, \$13 reserves 3 bytes w/ valves \$11, \$12 & \$13 at addr. assigned to ABC

- FDB form double-byte, same as FCB but 2 bytes per operand

- FCC form constant character

-stores ASCII code for alphanumeric characters enclosed in " " symbols

EX: NAME FCC "MIKE" stores 4 ASCII bytes for MIKE

## **Assembly Process**

Assembly Process: The process of converting ASM code into executable machine code.

Input ٠ .ASM code file, text .ASM (text file) ; Loop example for Ch. 3 notes by A.Mason. Mar 09 ; Sums 10 values from memory and store result in SUM. Outputs ; assumes 10 values to sum are stored at \$1000 .LST \_ ; assumes prior sum stored at SUM ORG \$4000 compiled code I DX #\$1000 ;set x to fist memory address program addresses & op-codes LDAB SUM ;load staring sum into accB LDAA #\$00 initialize counter to 0 .S19 record CHECK CMPA #\$0A ; ?added all 10? HEX file that can be uploaded to BEQ DONE ifyes, done ADDB if no, add # to SUM 0,X μC to store program to memory incrementIX INX INCA ;increment counter Testing paths • BRA CHECK repeatloop Simulator STAB DONE SUM store result EQU SUM \$4400 Test on hardware Idea END Flow Chart Write Code Editor ASM text Assemble Assembler LST compiled cod Υ Syntax Assembler Error? Ν Download to Simulator Debug **Eval Board** Hardware Debug Monitor .S19 machine code record, binary Logic S0030000FC Υ S1134000CE1000F644008600810A2706EB00084221 Error? S108401020F67B4400D2 S9030000FC Ν Done .LST compiled file, text Label Notes Op Code Mnemo Line Addr 1: ; Loop example for Ch. 3 notes by A.Mason. Mar 09 2: ; Sums 10 values from memory & store result in SUM з: assumes 10 values to sum are stored at \$1000 2 4: ÷ assumes prior sum stored at SUM 5: =00004000 \$4000 ORG 6: 4000 CE 1000 LDX #\$1000 ;set x to fist memory addr 7: 4003 F6 4400 LDAB SUM ;load staring sum into accB 8: 4006 86 00 LDAA #\$00 ; initialize counter to 0 9: 4008 81 OA CHECK CMPA #\$0A ; ?added all 10? 10: 400A 27 06 BEO DONE ; if yes, done if no, add # to SUM 11: 400C EB 00 ADDB ο,χ . 400E 08 INX ;increment IX 12: 13: 400F 42 INCA ;increment counter 14: 4010 20 F6 BRA CHECK ;repeat loop 15: 4012 7B 4400 DONE STAB SUM ;store result 16: =00004400 SUM EOU \$4400

END

17:

## **Assembly Process Example**

### **Assembly Code**

; ECE331 Example of SET/CLR Bit and Branch Instructions

### Assembled Code (.LST file)

| label <sup>1</sup> | mnemonic <sup>2</sup><br>directive <sup>1</sup> | operand <sup>3</sup>       | prog./data<br>mem. addr. <sup>4</sup> | machine opcode⁵ |

|--------------------|-------------------------------------------------|----------------------------|---------------------------------------|-----------------|

| ; main p           | rogram                                          |                            |                                       |                 |

| -                  | ORG                                             | \$4000                     | 4000                                  |                 |

|                    | LDAA                                            | #00                        | 4000                                  | 86 00           |

|                    | LDX                                             | #DATA                      | 4002                                  | CE 6000         |

| TOP                | BRSET                                           | A,X,\$01, <mark>ODD</mark> | 4005                                  | 0E E4 01 0B     |

|                    | BSET                                            | A,X,%00000011              | 4009                                  | 0C E4 03        |

|                    | BCLR                                            | A,X,%00001100              | 400C                                  | 0D E4 0C        |

|                    | LDAB                                            | A,X                        | 400F                                  | E6 E4           |

|                    | INCA                                            |                            | 4011                                  | 42              |

|                    | BRA                                             | ТОР                        | 4012                                  | 20 F1           |

| ODD                | SWI                                             |                            | 4014                                  | 3F              |

| ; data st          | orage                                           |                            |                                       |                 |

|                    | ORG                                             | \$6000                     | 6000                                  |                 |

| DATA               | FCB                                             | \$EE, \$DC, \$D0, \$F4     | 6000                                  | EE DC D0 F4     |

|                    | FCB                                             | \$80, \$00, \$55, \$22     | 6004                                  | 80 00 55 22     |

|                    | FCB                                             | \$AA                       | 6008                                  | AA              |

|                    | END                                             |                            |                                       |                 |

|                    |                                                 |                            |                                       |                 |

Notes:

- <u>Labels</u> and <u>Directives</u>: used by the assembler to simplify writing code and direct the assembly process. During assembly, all labels are replaced with appropriate hexadecimal values. Directives do not result in any program opcodes, although they can generate data to be stored in memory.

- <u>Mnemonics</u>: shorthand names for assembly instructions. Mnemonics will be converted to hexadecimal opcodes (machine code) during the assembly process that are loaded into microcontroller program memory to form the program that can be executed.

- 3. <u>Operands:</u> data parameters needed to complete a program instruction or assembly directive statement. Hexadecimal operands must be begin with a '\$' so the assembler knows the value is not a decimal. An operand with a '#' specifies an *immediate* address mode; otherwise the operand is an address. Multiple operands can be separated by comma or tabs, depending on the assembler used.

- 4. Once ASM code is assembled, all instructions and data are assigned to memory addresses. The addresses are determined by ORG directives in the ASM code. It is useful to differentiate between <u>program memory</u>, where instructions (and their operands) are stored and <u>data memory</u>, where non-instruction data fields are stored. Program memory contains the opcodes that will be fetched and decoded during program execution. Data memory contains data values read during program execution or results stored during program execution.

- 5. Operation codes, or machine <u>opcodes</u>, are hexadecimal values representing instructions. The binary equivalents of these codes tell the microcontroller exactly what do to. Assembly instruction opcode values will be stored in microcontroller program memory at the address indicated beside each line of opcode. For data directives, data values are stored directly to data memory at the address specified before the data values. Data values are not instructions and cannot be executed as program opcodes.

| Machine Code Upload Record (.S19 file)<br>S0030000FC<br>S11340008600CE60000EE4010B0CE4030DE40CE624 | \$0000 MCU<br>Registers 4000 86 top of<br>4001 00<br>4002 CE program |  |  |  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|--|--|

| S108 <mark>4010E44220F13F</mark> 31<br>S10C <mark>6000EEDCD0F480005522AA</mark> 64<br>S9030000FC   | Unused/<br>Reserved 4013 F1<br>4014 3F                               |  |  |  |

| Notes:                                                                                             | \$6000 Program                                                       |  |  |  |

| YELLOW HIGHLIGHTS show memory addresses<br>GREEN HIGHLIGHTS show data for data memory              | Data 6000 EE 6001 DC top of 6002 D0 data                             |  |  |  |

| BLUE HIGHLIGHTS show ASM program opcodes<br>to be stored in program memory                         | Unused/<br>Reserved                                                  |  |  |  |